# Fully digital and White Rabbit synchronized Low Level RF System for LIPAc

C. de la Morena, M. Weber, D. Regidor, P. Méndez, I. Kirpitchev, J. Mollá, A. Ibarra, M. Méndez, B. Rat, J.G. Ramírez, R. Rodríguez, J. Díaz

**Abstract**— The International Fusion Materials Irradiation Facility (IFMIF) is an international project to study and qualify candidate materials for the construction of a future fusion reactor. One of the objectives of the IFMIF-EVEDA (IFMIF-Engineering Validation and Engineering Design Activity) project is to build a Linear Prototype Accelerator (LIPAc) to validate the final IFMIF accelerator concept. LIPAc, which is currently under construction in Rokkasho (Japan), will generate a 9 MeV deuteron beam of 125 mA current with a 100% of duty cycle. CIEMAT (Spain) is in charge of providing the RF Power System, including the Low-Level Radio Frequency (LLRF) system.

Most of the developed LLRF systems are not completely digital, as they use analog front-ends for intermediate frequency (IF) conversion before or after digitalization. However, the LIPAc LLRF System is a fully digital system: no analog frequency conversion is performed, the radiofrequency (RF) signals are direct digitally synthesized and sampled by means of high speed DACs (Digital to Analog Converters) and ADCs (Analog to Digital Converters). This is a clear advantage in terms of flexibility, reliability, reconfigurability, cost, and response time, as all signal processing is performed in the digital domain. The other main advantage and novelty is the use of White Rabbit (WR) for timing synchronization and Master Oscillator distribution (distributed RF over WR, WR-DRF). LIPAc LLRF System is the first LLRF based on White Rabbit, and it has been designed and fabricated using the most advanced technology. This paper presents the detailed description of the LIPAc LLRF System, its advantages, performance evaluation, and verification.

**Index Terms**— Accelerator technology, accelerator control systems, accelerator RF systems, Low-level radio frequency, FPGA, digital signal processing.

## I. INTRODUCTION

After the migration of the LLRF Systems to In-Phase and Quadrature (I-Q) control in the 90's [1], traditional LLRF designs for accelerators have been based on the use of analog I-Q mod/demodulators for the RF signal generation/demodulation [2],[3]. The most widely adopted architecture

Manuscript received Xxxx, 2017. This work has been funded by the Spanish Government in the frame of the Broader Approach Agreement activities. Special thanks to our partner companies INDRA, JEMA, and Broad Telecom (BTESA).

C. de la Morena, M. Weber, D. Regidor, P. Méndez, I. Kirpitchev, J. Molla, and A. Ibarra are with the Fusion Technology Division, National Fusion Laboratory-CIEMAT, Avda. Complutense 40, 28040 Madrid, Spain (e-mail: cristina.delamorena@ciemat.es).

M. Méndez, B. Rat, J.G. Ramírez, R. Rodríguez, and J. Díaz are with Seven Solutions S.L., C/Periodista Rafael Gómez Montero 2, Oficina 13 Edf. CETIC, Granada, Spain (e-mail: mmendez@sevensols.com).

has been the homodyne or zero-IF, where the RF signal is directly down-converted to zero frequency by means of an I-Q demodulator and a local oscillator (LO) of the same frequency. After low-pass filtering, baseband I-Q components can be directly obtained (baseband sampling). Zero-IF architecture has some important limitations, such as DC-offset, 1/f noise, I-Q imbalances, LO leakage, and second-order intermodulation distortion [4]. However, it presents benefits with respect to heterodyne: there is no image frequency (therefore no costly image rejection filters are required), main operations are baseband performed, which leads to higher level of integration, compact size, simplicity, low-power consumption, flexibility, and system reconfigurability [5].

Migration toward digital systems and Software Defined Radio architectures is the trend at the present moment. In the last years, most of the LLRF systems have been upgraded to partially-digital architectures, which combine an analog heterodyne architecture with digital IF synthesis/IF sampling [6]-[9]. Zero-IF architectures have incorporated recent digital signal control and processing technologies, and they are still used in LLRF systems [10], mainly in the RF generation part combined with IF sampling [11]-[18]. Nevertheless, in general terms and in particular for linear accelerators applications, LLRF Systems performance continues to be limited mainly by analog components, especially for high frequency applications, where it is not possible to eliminate analog frequency conversion circuits before or after digitalization, due to current state-of-art on DACs/ADCs.

A first half-digital LLRF prototype was developed by CIEMAT in collaboration with CELLS [19]-[20]. It was based on direct digital demodulation (direct sampling), but for RF signal generation an analog front-end was used for up-conversion from IF to final RF.

The LIPAc LLRF System described in this paper is a novel, fully digital, and WR synchronized LLRF System, where both RF signal generation and demodulation are fully performed in the digital domain. IFMIF demands very challenging requirements for the LLRF and RF systems, especially regarding flexibility, synchronization, RF field detection precision, signal stability, and RAMI (Reliability, Availability, Maintainability and Inspectability) [21]. Some main specifications for the LIPAc LLRF System are compiled in Table 1. Note that extra flexibility is required not only in the RF operational regime (continuous and pulsed), but also in the

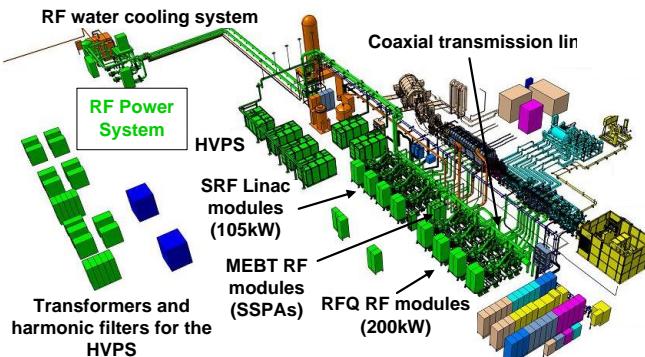

Fig. 1. 3D schematic of the LIPAc RF Power System.

LLRF output frequency, which has to be dynamically shifted  $\pm 300\text{kHz}$ . In order to fill the cavities when they are not tuned to the nominal frequency, and the cavity tuning systems are too slow to reach tuning condition, the LLRF dynamically changes its frequency to follow the cavity resonance frequency. This is required in two situations: during the start-up of the RFQ cavity, where the power increases up to 200 kW, and the power dissipation produces a temperature increment that modifies the cavity resonance frequency; and for beam loading compensation in pulse mode operation, in order to pre-fill the cavities before the beam arrival (the tuning systems keeps the cavities tuned to the nominal frequency when there is beam and therefore they are detuned before the beam arrival). Another challenging specification is the synchronization of several RF chains in order to operate as a unique chain, coincident in time and with the same amplitude and phase. Consequently, many efforts have been focused on the development of a robust, innovative, and cutting-edge LLRF System, capable to fulfill very demanding specifications. A complete digital and WR-compliant design multiplies the advantages and possibilities, as it will be explained in sections III and IV, where the main characteristics and innovations of the LIPAc LLRF System will be presented. LLRF is part of the LIPAc RF Power System, which will be briefly described in Section II. The measured performance and validation test of the LLRF system will be presented in Section IV.

TABLE I LIPAC LLRF SYSTEM MAIN REQUIREMENTS

| Parameter                             | Value/description                                                                        |

|---------------------------------------|------------------------------------------------------------------------------------------|

| Cavity types                          | 1 RF Quadrupole (RFQ)<br>2 re-buncher cavities<br>8 superconducting half-wave resonators |

| Nominal Frequency                     | 175 MHz                                                                                  |

| Frequency shift                       | $\pm 300\text{ kHz}$ , for real-time cavity resonance frequency tracking                 |

| Stability (closed loop)               | $\pm 1\%$ in amplitude<br>$\pm 1^\circ$ in phase                                         |

| RF operational regime                 | CW and pulsed mode                                                                       |

| Emergency RF stop                     | $< 10\text{ }\mu\text{s}$ (at the cavity input)                                          |

| Cavity tuning                         | 1° resolution                                                                            |

| RF chains balance and synchronization | Amplitude/phase balance and time synchronization to operate as a unique RF chain         |

| RAMI                                  | 98.2% availability                                                                       |

## II. LIPAC RF POWER SYSTEM

The LIPAc RF Power System [21]-[25] consists of 18 RF chains operating at 175 MHz, 12 400 kW high voltage power supplies (HVPS), 18 coaxial transmission lines to reach the accelerator cavities, and the water cooling system primary circuit. The 3D view of the LIPAc accelerator is presented in Fig. 1, where all RF System components are represented in green color.

The 18 RF chains are structured in 9 RF modules (two RF chains form one RF module), and are distributed as follows:

- Eight 200 kW RF chains (four 2x200kW RF modules) for the RFQ.

- Two 16 kW RF chains (one 2x16kW RF module) for the two re-buncher cavities of the Medium Energy Beam Transport (MEBT).

- Eight 105 kW RF chains (four 2x105kW RF modules) for the eight superconducting half-wave resonators of the SRF Linac.

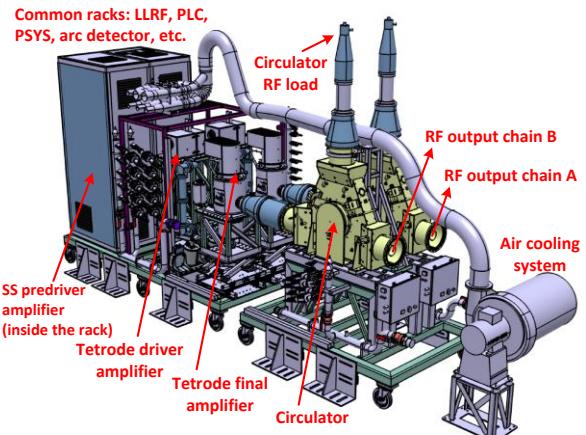

For standardization and scale economy reasons, the 200kW and 105kW RF chains share the same topology and main components, and they only differ in the circulator. They consist of three amplification stages: a first solid-state pre-driver, and two tetrodes for driver and final amplifiers. Two RF chains compose one RF module, as they share some common elements such as the mechanical structure for the circulators and tetrodes, the water and air cooling circuits, the LLRF unit, the PLC (Programmable Logic Controller), the arc detector system, the protection system, etc. Tetrode RF modules for RFQ and SRF Linac have been developed by CIEMAT and its partner company INDRA, under CIEMAT conceptual design. **The 3D-mock-up of the tetrode-based RF module is represented in Fig. 2.**

The 2x16 kW RF module for MEBT is based on solid state (SS) technology, and can be seen in Fig. 3. Each RF chain contains two SS amplification stages: a first predriver amplifier, and a final amplifier, which is formed by the combination of 10 SS Power Amplifiers (PA). Both RF chains share some common elements (LLRF, arc detector, PLC, etc). The detailed design and fabrication of the SS RF module are made by the Spanish company Broad Telecom (BTESA) under CIEMAT conceptual design.

Fig. 2. Tetrode-based RF module.

Fig. 3. Solid-state 2x16kW RF module.

The 400 kW HVPSs (up to 13 kV and 45 A) for the tetrode-based amplification changes are designed and manufactured by JEMA Energy (San Sebastián, Spain).

### III. LIPAC LLRF SYSTEM DESCRIPTION

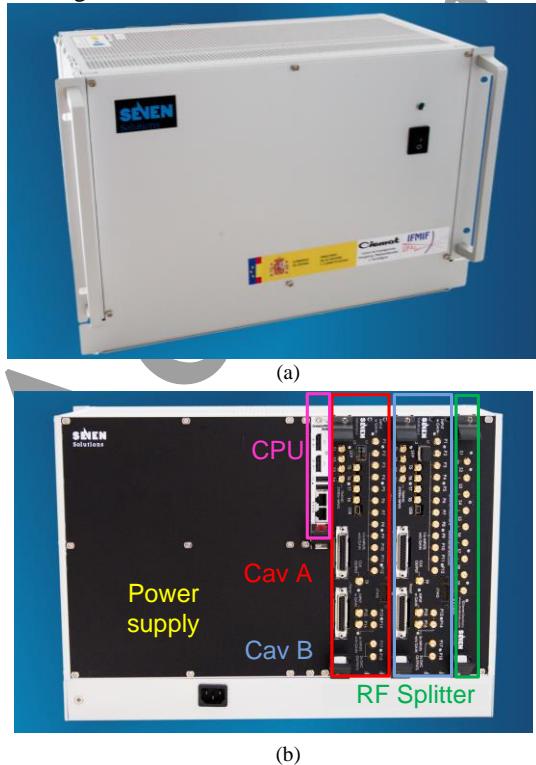

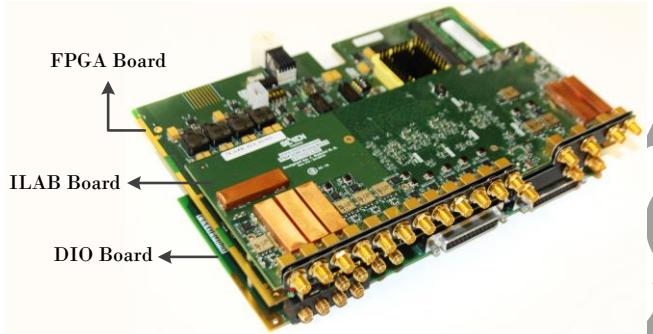

The LIPAC LLRF system consists of nine LLRF units. A photograph of one LLRF unit is shown in Fig. 4. It can be also seen integrated in one rack of the solid-state 2x16kW RF module in Fig. 3.

Fig. 4. LLRF unit: (a) front view, (b) rear view.

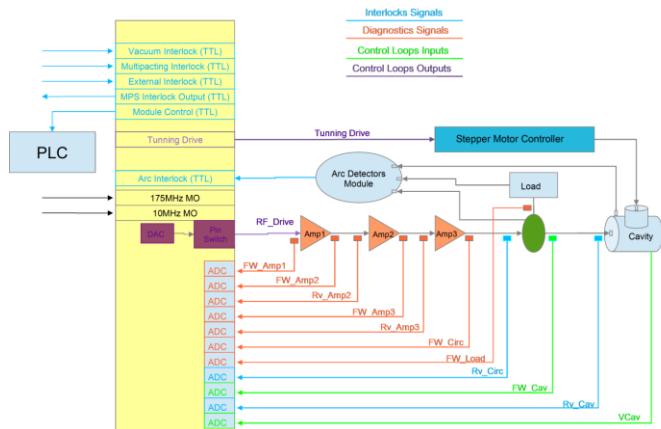

Each LLRF unit is designed to control two RF cavities. Fig. 5 shows the LLRF block diagram with the different elements and connections needed to control one RF cavity. The main implemented functionalities are described below:

- Cavity field amplitude and phase control (feedback loop).

- Signal diagnostics and data remote access.

- Cavity tuning: manual and automatic.

- Conditioning: manual and automatic.

- Fast interlock management: arcs, reflected power, max. forward power, multipacting, vacuum, etc.

- Continuous wave (CW) and pulse operation modes.

- Frequency modulation: manual and automatic.

- Feed-forward loop: cavity pre-filling, beam loading compensation.

- Timing synchronization and Master Oscillator distribution using White Rabbit (WR-DRF).

- Fast data logger for post mortem analysis.

- Automatic start-up.

- Master-slave feedback loop (specific for RFQ): synchronization of the eight RFQ RF chains to operate as a unique chain, one as master and seven as slaves.

- Temperature dependence compensation.

#### A. Hardware description

The LLRF unit is a compact and fully integrated system. It is based on a modular design, as shown in Fig. 4, where the different boards can be easily extracted and substituted in order to improve the availability. Each LLRF unit is composed of:

- One Compact-PCIe Serial (cPCI-S) rack enclosure.

- One cPCI-S backplane.

- One 200W Power Supply.

- One cPCI-S CPU (G20-3U CompactPCI® Serial Intel® Core™ i7 CPU Board).

- Two 6U integrated-board modules, composed of several boards arranged in a sandwich distribution. Each integrated-board module controls one cavity and performs all the described functionalities. It is described in more detail in Section IV.

- One 6U 1:8 RF splitter (specific for RF Quadrupole).

Fig. 5. LLRF Block diagram for one cavity control.

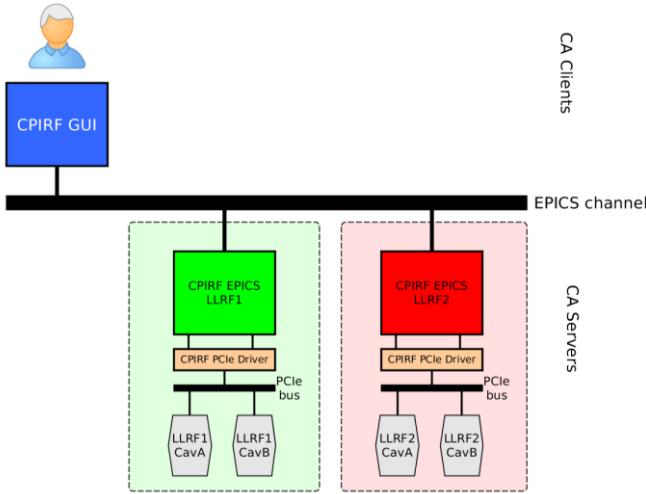

### B. Software architecture

LIPAc LLRF control system is based on the Experimental Physics and Industrial Control System (EPICS). EPICS is a software environment used to develop and implement distributed control systems to operate devices such as particle accelerators, telescopes, and other large experiments. EPICS control systems work with a Client/Server architecture. Fig. 6 shows a schematic of the LLRF software architecture.

Fig. 6. LLRF Software Architecture.

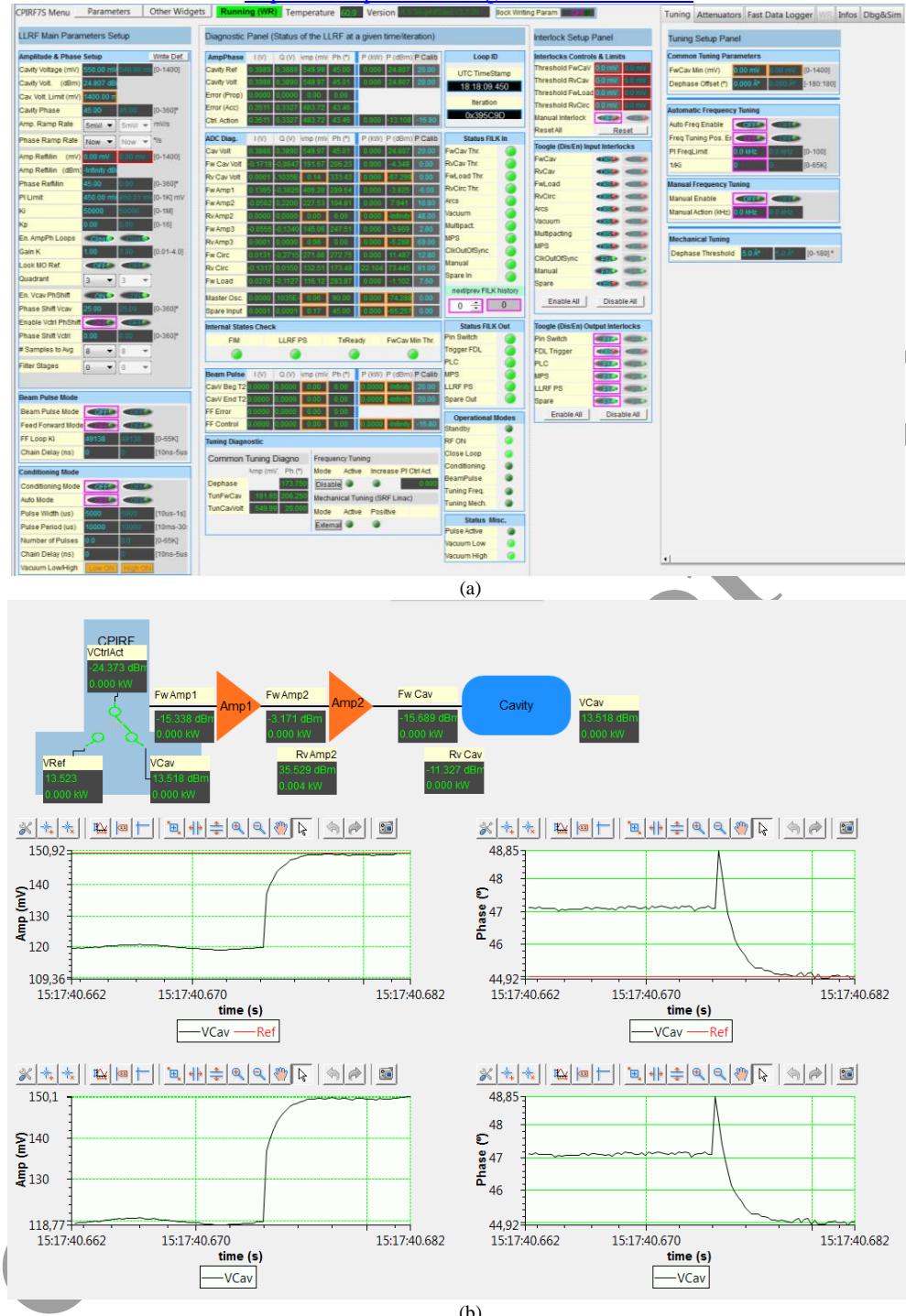

### C. User interface

The graphical user interface (GUI) has been developed using CSS BOY (see Fig. 8). The design takes into account the previous experience of the different European Institutes involved in the LIPAc project, which have elaborated some recommendations and standards that follow basic rules such as simplicity, efficiency, intuitive structure, user friendly environment, etc.

### D. White Rabbit

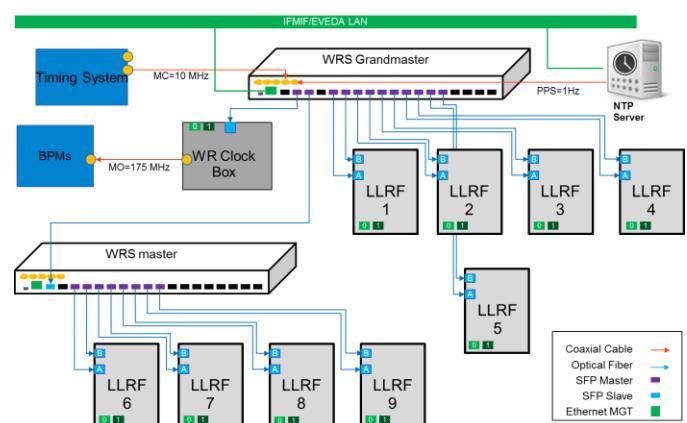

The generation and distribution of the timing reference signals is crucial for preserving the synchronization into an accelerator facility. The LIPAc Timing System, which is developed by QST (Japan), provides the 10 MHz Master Clock (MC) signal to the different accelerator systems, including the RF System. CIEMAT is in charge of distributing the MC to the overall RF System, keeping signal integrity and synchronization among the 18 RF chains. Furthermore, CIEMAT is responsible of the generation and distribution of the 175 MHz Master Oscillator (MO) reference signal. The MO has to be a very stable signal locked to the MC, in order to act as timing reference for the accelerator sub-systems. MO is required at each LLRF and also at some external systems like the Beam Position Monitors (BPMs).

The classical solution consists of generating both MC and MO signals by means of phase-locked high quality signal generators, and split these signals using well-balanced analog distribution networks with conventional coaxial cables. This solution is problematic because it is very sensitive to environmental conditions, temperature fluctuations, humidity

changes, material aging, losses variations, calibrations exactness, etc. Consequently, with this configuration it is difficult in practice to achieve a perfect balance among all branches and therefore high-precision synchronization. Another drawback is that a high isolation is required in the coaxial cables, since they cross very emissive environments in an accelerator facility. Alternatively, CIEMAT and Seven Solutions have developed a timing distribution and synchronization system based on WR for both MC and MO reference signals, whose scheme is shown in Fig. 7. It consists of one Master WR Switch and one Slave WR Switch, which communicates with the nine WR-compliant LLRF units by optical fibers. Optical technology has clear benefits for synchronization reference distribution for large facilities, as it provides less signal attenuation and larger bandwidths, and alleviates the above mentioned problems of conventional coaxial cables. For not-compliant WR devices, such as the BPMs in LIPAc, the WR synchronization system includes a WR Clock Box, which is connected by optical fiber to the WR node, and provides a stable MO (phase noise<1ps) through coaxial cable.

WR is a fully deterministic Ethernet-based network that provides ultra-accurate synchronization and gigabit data transfer capability. It was born in CERN for time and frequency dissemination, and it has been conceived to fulfill the following goals:

- Time precision: WR technology provides a common clock for physical layer in the entire network, allowing synchronization at sub-nanosecond level with picoseconds precision.

- Scalability: the WR network is designed to be highly scalable to support thousands of nodes. It also intends to be as modular as possible, and compatible with non-WR devices.

- Distance range: taking into account the size and ranges of the majority industrial and scientific facilities, the WR network specifications have been designed to support distances up to several tens of kilometers between nodes.

Fig. 7. Timing reference distribution using White Rabbit.

Fig. 8. LLRF Graphical User Interface (a) main view (b) example of diagnostic.

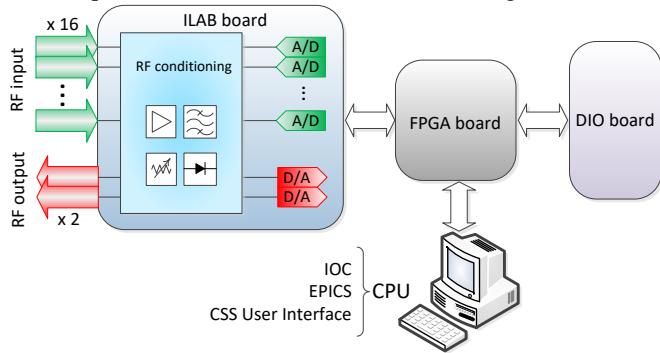

#### IV. DIRECT DIGITAL RF SYNTHESIS AND DEMODULATION

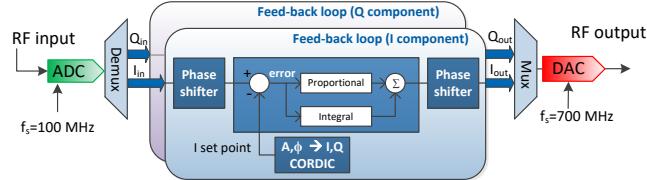

The LIPAc LLRF is a fully digital system, where both RF synthesis and demodulation are completely performed in the digital domain. The system concept is shown in Fig. 9. Focusing on the RF demodulation part, undersampling technique, also known as direct bandpass sampling, is used for the 175MHz signal acquisition and the in-phase (I) and quadrature (Q) components detection (sampling frequency  $f_s=100$  MHz). Regarding the RF generation side, two 175MHz

signals are directly generated by means of fast DACs, working at  $f_s=700$  MHz. Let us represent the RF signal in terms of its I/Q components as follows:

$$v(t) = I \cdot \cos(2\pi f_c t) - Q \cdot \sin(2\pi f_c t) \quad (1)$$

where  $f_c$  is the nominal 175 MHz frequency, and  $t$  is the time. The digitalized signal results in:

$$v\left(\frac{n}{f_s}\right) = I \cdot \cos\left(2\pi f_c \cdot \frac{n}{f_s}\right) - Q \cdot \sin\left(2\pi f_c \cdot \frac{n}{f_s}\right) \quad (2)$$

being  $n=0,1,2,\dots$ . Notice that the factor  $f_c/f_s = 1.75$  has been

selected for the demodulation, which substituted in (2) results in the sequence: I, Q, -I, -Q, I, Q, ... For the RF generation, the

Fig. 9. System schematic description: direct RF signal synthesis/acquisition.

Fig. 10. Feed-back loop block diagram.

Fig. 11. Photograph of the integrated-board module.

relation  $f_s/f_c$  is 1/4, which leads to: I, -Q, -I, Q, I, -Q, ... Note that the I-Q components can be easily obtained by demultiplexing/multiplexing the samples, and applying a phase inversion. Using such multiples of 175MHz is very advantageous, as the FPGA can work directly with I/Q components, which simplifies the signal processing and reduces the FPGA computational load.

The cavity field feedback loop is a Proportional-Integral (PI) loop that applies directly to I/Q components, whose block diagram is presented in Fig. 10. Amplitude and phase values can be easily obtained from IQ components as follows:

$$A = \sqrt{I^2 + Q^2} \quad (3)$$

$$\phi = \text{atan}\left(\frac{Q}{I}\right) \quad (4)$$

These operations are carried out in the FPGA by means of the CORDIC algorithm.

Each board shown in Fig. 9 is arranged in a sandwich distribution forming an integrated-board module (see Fig. 11), composed of:

- 1) ILAB board: it integrates a RF conditioning front-end and fast ADCs/DACs. The RF front-end is a signal adaptation

stage, without analog frequency conversion, which contains:

- 16 SMA input channels: based on filters, and SW controllable attenuators. There are two channels with additional amplification, dedicated for low power RF signals.

- 2 SMA output channels: based on filters, SW controllable attenuators, amplifiers, and absorptive pin diode switches for fast RF stop.

Connected to these RF conditioning paths, there are 2 DACs (1.25 Gsps, 16 bits, -60 to +14 dBm dynamic range), and 16 ADCs (125 Msps, 14 bits, -40 to +17 dBm dynamic range). ILAB board is connected to the FPGA board by a double FMC (FPGA Mezzanine Card).

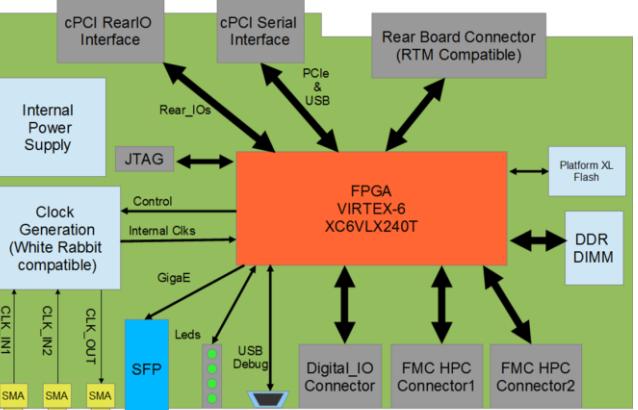

- 2) FPGA board: based on Xilinx Virtex-6 (LX240T) FPGA and a 2GB DDR DIMM (Double Data Rate, Dual In-line Memory Module). Its block diagram is shown in Fig. 12. It includes the Clock Generation block, which is responsible of providing the different clocks to the system, using a high-performance VCXO (Voltage-Controlled Crystal Oscillator), and a Phase-Locked Loop (PLL).

- 3) Digital Input/Output (DIO) board: digital I/O signals (DB-25 connectors) for interlocks, cavity tuning signals, and other communications with external subsystems. Timing System trigger/gate signals (SMA) for beam synchronization.

Fig. 12. Block diagram of the FPGA board.

## V. LLRF PERFORMANCE AND VALIDATION

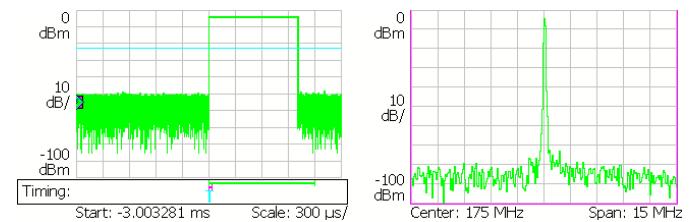

All the LLRF functionalities described in Section III have been satisfactorily proved and validated. Table 2 summarizes the basic main performance of LLRF system in stand-alone mode (not connected to the RF chains). The system can operate in CW and pulsed regime (min. 10  $\mu$ s pulse width). The nominal output frequency is 175 MHz, which can be dynamically shifted  $\pm 300$  kHz to compensate cavity detuning, in manual or automatic mode (cavity resonance frequency tracking). It is observed a good quality of the LLRF 175 MHz output signal, which is locked to the MO reference distributed by WR: <-60 dBc harmonics rejection, and <-65 dBc spurious rejection. The output power can be selected between -60 dBm and 14 dBm (74 dB dynamic range). A very good RF signal

stability, which is a main parameter for LLRF systems, has been achieved when working in stand-alone closed feedback loop (direct wire connection between LLRF RF output and input): 0.08° of rms phase variation (100 Hz-1 MHz), and 0.0051% rms variation in voltage amplitude. Another important parameter is the emergency RF stop, that is, the time between an alarm is detected and the RF output signal is switched off. The measured emergency RF stop time is only 800 ns in stand-alone mode.

TABLE 2 LLRF BASIC PERFORMANCE (STAND-ALONE)

| Parameter           | Measured value     |

|---------------------|--------------------|

| Operational regime  | CW/pulsed          |

| Nominal frequency   | 175 MHz            |

| Frequency shift     | ± (0.1 – 300) kHz  |

| Output power        | -60 dBm to +14 dBm |

| Amplitude stability | 0.0051% rms        |

| Phase stability     | 0.08° rms          |

| Harmonics level     | <-60 dBc           |

| Spurious level      | <-65 dBc           |

| Emergency RF stop   | ~ 800 ns           |

The LLRF has been integrated and validated with the LIPAc high power RF modules in Madrid (Spain), at INDRA and BTESA facilities. Currently, the RF modules for RFQ and MEBT are installed in Rokkasho (Japan), where they are being commissioned [26]. Table 3 compares the LIPAc RF Power System requirements with the measured performance for one 200 kW tetrode-based RF chain, while Table 4 presents the results for one 16 kW solid-state RF chain. As it can be seen, all parameters fulfill the specified requirements. Similar results are obtained in the rest of RF chains.

TABLE 3 2<sup>ND</sup> RFQ 2x200 kW RF MODULE: CHAIN A PERFORMANCE

| Parameter                         | Acceptance Criteria | Measured value                                                  |

|-----------------------------------|---------------------|-----------------------------------------------------------------|

| Frequency                         | 175 MHz             | 175 MHz                                                         |

| Bandwidth                         | ±250 kHz @ -1dB     | -0.18dB @ 250 kHz                                               |

| Phase stability (closed loop)     | ±1°                 | 0.0945° rms                                                     |

| Amplitude stability (closed loop) | ±1%                 | ±0.26 peak (*)                                                  |

| Output RF power                   | 200 kW CW           | 220 kW CW > 20 h                                                |

| Full reflected power              | 10 µs               | Full reflection (200kW): 100 ms                                 |

| Maintained reflected power        | 20 kW, 2h           | 40kW > 2h                                                       |

| Operating mode                    | CW                  | CW. Also validated in pulsed mode (from 2 µs pulse width to CW) |

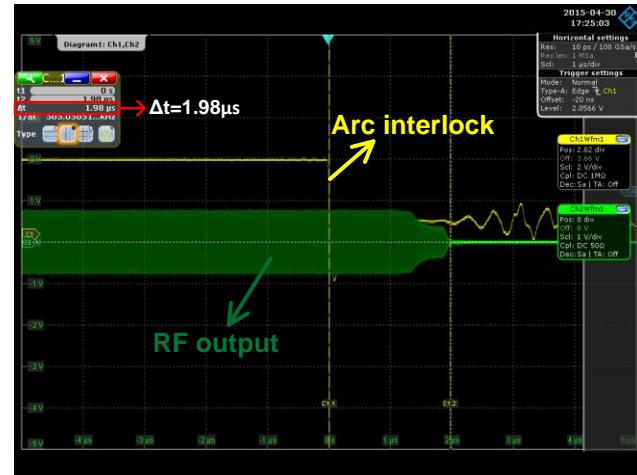

| Emergency RF stop                 | < 10 µs             | 1.98 µs                                                         |

| Harmonics Level                   | < -30 dBc           | -51.17 dBc                                                      |

| Spurious Level                    | < -30 dBc           | <-75 dBc                                                        |

(\*) Peak error

Focusing on the parameters that are more related to LLRF performance, it is important to pay attention to the amplitude and phase signal stability results. RF signal stability is crucial for accelerators performance, and very good results have been

achieved. A 0.0945° rms phase error is obtained for the 200kW RF chain, and 0.13° rms for the SS 16 kW chain. The phase error has been quantified in terms of the phase jitter (°rms), which can be obtained from the phase noise

TABLE 4 SOLID STATE 2x16kW RF MODULE: CHAIN A PERFORMANCE

| Parameter                         | Acceptance Criteria | Measured value                                                  |

|-----------------------------------|---------------------|-----------------------------------------------------------------|

| Frequency                         | 175 MHz             | 175 MHz                                                         |

| Bandwidth                         | ±250 kHz @ -1dB     | -0.04dB @ 250 kHz                                               |

| Phase stability (closed loop)     | ±1°                 | 0.13° rms                                                       |

| Amplitude stability (closed loop) | ±1%                 | ±0.16% peak (*)                                                 |

| Output RF power                   | 16 kW CW            | 16 kW CW > 12 h Max. 20 kW                                      |

| Full reflected power              | 10 µs               | Full reflection (16kW): 120 ms                                  |

| Maintained reflected power        | 4 kW, 2h            | 4.8kW > 2h                                                      |

| Operating mode                    | CW                  | CW. Also validated in pulsed mode (from 2 µs pulse width to CW) |

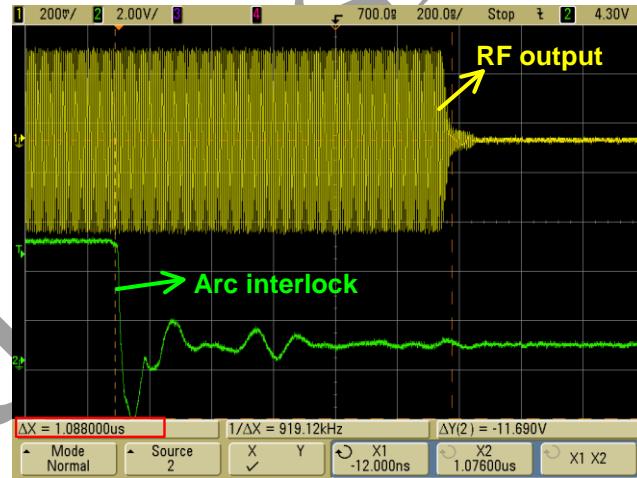

| Emergency RF stop                 | < 10 µs             | 1.08 µs                                                         |

| Harmonics Level                   | < -30 dBc           | -42.62 dBc                                                      |

| Spurious Level                    | < -30 dBc           | -70.67 dBc                                                      |

(\*) Peak error

TABLE 5 PHASE NOISE MEASUREMENTS (SS 16 kW CHAIN)

| Freq. offset        | Phase noise (dBc/Hz) |

|---------------------|----------------------|

| 100 Hz              | -92                  |

| 1 kHz               | -105                 |

| 10 kHz              | -109                 |

| 100 kHz             | -109                 |

| 1 MHz               | -127                 |

| Phase jitter (°rms) | 0.13                 |

TABLE 6 AMPLITUDE STATISTICAL DISPERSION PARAMETERS

| Parameter                       | 200 kW RF chain | 16 kW SS chain |

|---------------------------------|-----------------|----------------|

| Observation time                | 2 hours         | 2 hours        |

| Num. of samples                 | 7753            | 1463           |

| Range (Max - Min)               | 0.34%           | 0.28%          |

| Standard deviation ( $\sigma$ ) | 0.087%          | 0.055%         |

| Peak error ( $\pm 3\sigma$ )    | ±0.26%          | ±0.16%         |

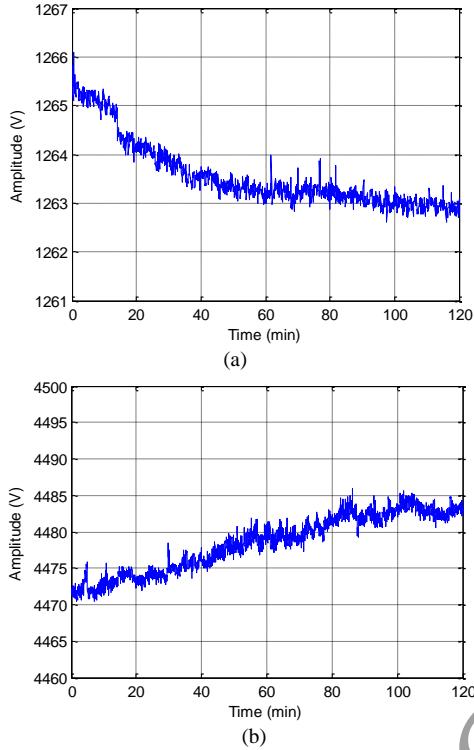

measurements [27]. For the 200 kW chain, the measurement has been automatically performed using the R&S®FSU3 Spectrum Analyzer (option R&S®FS-K40). For the SS 16 kW chain, the phase noise measurements compiled in Table 5 have been used. In regard to the amplitude stability test, the RF chains were kept at maximum power during two hours, meanwhile the amplitude of the RF signal was measured by a power meter (Agilent N1914A power meter and high precision N8482A sensors, no averaging applied), and the data were transferred to a Personal Computer. The measured voltage amplitude with respect to time is plotted in Fig. 13. Statistical results for voltage amplitude variation, calculated from the measured data, are shown Table 6. Peak voltage amplitude error has been calculated considering the three-sigma rule: 99.7% of cases are taken to lie within  $\pm$  three standard

deviations ( $\pm 3\sigma$ ) from the mean, which can be empirically treated as near certainty. Consequently, the results are  $\pm 0.26\%$  for the 200kW RF chain, and  $\pm 0.16\%$  in the 16 kW SS chain. Note that this convention is more pessimistic than the range given by the measured maximum and minimum values. In any case, these figures are quite smaller than the requirement of  $\pm 1\%$ .

Fig. 13. Voltage amplitude variation versus time: (a) solid state 16 kW RF chain; b) tetrode-based 200 kW RF chain.

Another important parameter for accelerators is the emergency RF stop. In these measurements it is considered the time between an alarm is detected in the LLRF, and the RF at the output of the RF chain is switched off (it includes RF chain propagation delay). Note that LIPAc requirement is  $<10\ \mu\text{s}$ , and the measured emergency RF stop is  $1.98\ \mu\text{s}$  and  $1.08\ \mu\text{s}$  for the 200kW and 16kW chains, respectively (see Fig. 14 and Fig. 15).

Fig. 14. Emergency RF stop: tetrode-based 200kW RF chain.

Fig. 15. Emergency RF stop: solid state 16kW RF chain.

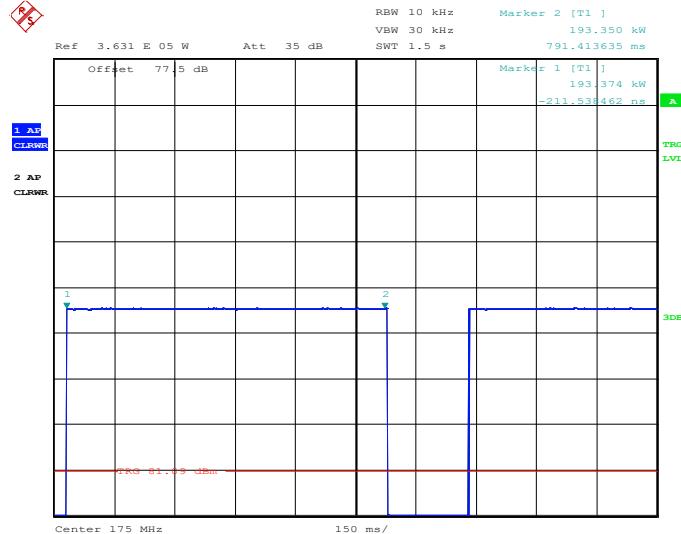

The LLRF can operate in CW and pulse modes. Some examples of the pulse mode operation are shown in Fig. 16 and Fig. 17.

Last but not least, the RF signal quality at the output of the RF chains is good, as it can be seen from the harmonics and spurious rejection measurements in Table 3 and Table 4.

Fig. 16. Pulse mode operation example: 1ms width, 100ms period (solid state 16kW RF chain).

Fig. 17. Pulse mode operation example: 800ms width, 1s period (tetrode-based 200kW RF chain).

## VI. CONCLUSION

The LLRF system for the IFMIF-EVEDA project has been developed and integrated into the LIPAc RF Power System. It has been validated operating with high-power RF chains, exceeding its design specifications. The main advantages and novelties of the LLRF system are presented below:

- Fully digital LLRF: Direct digital synthesis and direct digital sampling (high speed DACs and ADCs). No external front-ends are used for frequency conversion.

- Timing and synchronization based on White Rabbit (CERN). Sub-nanosecond synchronization.

- WR Master Oscillator distribution (WR-DRF).

- Modular design with all functionalities integrated in the same unit.

- Flexible, reconfigurable, and customizable system.

- Fully digital signal processing. Flexible nominal frequency without hardware modifications.

- EPICS ready technology.

- Use of advanced FPGA technology (Xilinx Virtex-6).

- Both MicroTCA and cPCI platforms available.

- Configurable Analog Input module to receive different input signal levels.

All this characteristics traduce in a very flexible and reconfigurable system, where many improvements and modifications can be performed without HW changes, just via firmware: new functionalities, improved and faster control loops, operation frequency migration, fast and efficient frequency modulation, etc. It is worth to mention that the maximum operating frequency in a digital approach is restricted by the performance of state-of-art DAC/ACS, being the main limiting factors the sampling frequency, the resolution, and the jitter.

## REFERENCES

- [1] S. P. Jachim, "Some New Methods of RF Control," in *Proceedings of the 1990 Linear Accelerator Conference*, 1990, pp. 573–577.

- [2] A. H. Regan, D. Brittain, D. E. Rees, and C. D. Ziomek, "RF System Description for the Ground Test Accelerator Radio-Frequency Quadrupole," in *Proceedings of the 1992 Linear Accelerator Conference*, 1992, pp. 680–682.

- [3] A. Young, L. E. Eaton, and L. Alamos, "RF system specifications for a linear accelerator\*," in *Proceedings of the 1992 Linear Accelerator Conference*, 1992, pp. 121–123.

- [4] B. Razavi, "Design considerations for direct-conversion receivers," *IEEE Trans. Circuits Syst. II Analog Digit. Signal Process.*, vol. 44, no. 6, pp. 428–435, 1997.

- [5] C. de La Morena-Álvarez-Palencia and M. Burgos-García, "Experimental performance comparison of six-port and conventional zero-IF/low-IF receivers for Software Defined Radio," *Prog. Electromagn. Res. B*, vol. 42, no. July, pp. 311–333, 2012.

- [6] M. Champion, M. Crofford, K. Kasemir, H. Ma, M. Piller, L. Doolittle, and A. Ratti, "Overview of the Spallation Neutron Source Linac Low-Level RF control system," in *Proceedings of the IEEE Particle Accelerator Conference*, 2005, pp. 3396–3398.

- [7] A. Fabris et al., "The LLRF System for the S-Band RF Plants of the FERMI Linac," in *IEEE Transactions on Nuclear Science*, vol. 63, no. 2, pp. 861–868, April 2016.

- [8] J. Branlard, B. Chase, E. Cullerton, P. Joireman, and V. Tupikov, "LLRF Design for the Hins-Srf Test Facility At Fermilab," in *LLRF design for the HINS-SRF test facility at Fermilab*, 2010, pp. 247–249.

- [9] T. Plawski, R. Bachimanchi, C. Hovater, D. Seidman, M. Wissmann, and N. News, "LLRF system for the CEBAF separator upgrade," in *Proceedings of Linear Accelerator Conference LINAC2014*, 2014, pp. 1171–1173.

- [10] A. Araz, U. Bonnes, R. Eichhorn, F. Hug, M. Konrad, M. Platz, A. Richter, and R. Stassen, "3 GHz digital rf control at the superconducting Darmstadt electron linear accelerator: First results from the baseband approach and extensions for other frequencies," *Phys. Rev. Spec. Top. - Accel. Beams*, vol. 13, no. 8, pp. 1–6, 2010.

- [11] V. Ayvazyan, K. Czuba, Z. Geng, M. Grecki, O. Hensler, M. Hoffmann, T. Jezynski, W. Koprek, F. Ludwig, K. Rehlich, H. Schlarb, C. Schmidt, S. N. Simrock, and H.-C. Weddig, "LLRF control system upgrade at FLASH," in *Proceedings of PCaPAC 2010*, 2010, pp. 150–152.

- [12] P. Baudrenghien, G. Hagemann, J. C. Molendijk, R. Olsen, T. Rohlev, V. Rossi, D. Stellfeld, D. Valuch, and U. Wehrle, "The LHC Low Level RF," in *Proceeding of EPAC 2006*, 2006, pp. 1471–1473.

- [13] K. Pozniak, A. Brandt, M. Hoffmann, W. Koprek, P. Pucyk, S. Simrock, and R. S. Romanik, "Measurement and control of field in RF GUN at FLASH," *Proc. SPIE 6937, Photonics Appl. Astron. Commun. Ind. High-Energy Phys. Exp.* 2007, vol. 69370F, 2007.

- [14] M. Smelkowski, P. Strzalkowski, and K. T. Pozniak, "Vector modulator board for X-FEL LLRF system," *Proc. SPIE 6937, Photonics Appl. Astron. Commun. Ind. High-Energy Phys. Exp.* 2007, vol. 69370L, 2007.

- [15] Z. Fang, S. Anami, S. Michizono, T. Kobayashi and H. Suzuki, "RF feedback control systems of the J-PARC LINAC," *2007 IEEE Particle Accelerator Conference (PAC)*, Albuquerque, NM, 2007, pp. 2101–2103.

- [16] Z. Fang, K. Futatsukawa, Y. Fukui, T. Kobayashi, S. Michizono, F. Sato, S. Shinozaki, and E. Chishiro, "Present status of J-PARC LINAC LLRF systems," in *Proceedings of Linear Accelerator Conference LINAC2014*, 2014, pp. 3–5.

- [17] I. Rutkowski et al., "MTCA.4-Based Digital LLRF Control System for CW SRF Linacs," in *IEEE Transactions on Nuclear Science*, vol. 62, no. 6, pp. 3186–3192, Dec. 2015.

- [18] A. Hauff, M. Brönnimann, I. Brunnenkant, A. Dietrich, F. Gärtner, Z. Geng, M. Jurcevic, R. Kalt, S. Mair, A. Rezaiezadeh, L. Schebacher, T. Schilcher, and W. Sturzenegger, "SwissFEL C-band LLRF Prototype System," in *Proceedings of Linear Accelerator Conference LINAC2014*, 2014, pp. 683–685.

- [19] A. Salom, A. Arriaga, J. Calvo, I. Kirpitchev, P. Méndez, D. Regidor, M. Weber, A. Mosnier, and F. Perez, "Digital LLRF for IFMIF-EVEDA," in *Proceedings of IPAC 2011*, 2011, pp. 457–459.

- [20] J. Calvo, M. L. Rivers, M. a. Patricio, and A. Ibarra, "EPICS based low-level radio frequency control system in LIPAc," *Fusion Eng. Des.*, vol. 87, no. 11, pp. 1872–1879, 2012.

- [21] E. Bargallo, a. Giralt, G. Martinez, M. Weber, D. Regidor, J. M. Arroyo, J. Abal, J. Dies, C. Tapia, a. De Blas, P. Mendez, a. Ibarra, and J. Molla, "Availability, reliability and logistic support studies of the RF power system design options for the IFMIF accelerator," *Fusion Eng. Des.*, vol. 88, no. 9–10, pp. 2732–2735, 2013.

- [22] D. Regidor et. al., "IFMIF-EVEDA RF Power System," in *Proceedings of IPAC 2011*, 2011, pp. 394–396.

- [23] M. Weber, D. Regidor, C. de la Morena, P. Mendez, J. M. Arroyo, I. Kirpitchev, J. Molla, and A. Ibarra, "RAMI optimization-oriented design for the LIPAc RF Power System," in *Proceedings of IPAC 2015*, 2015.

- [24] J. Knaster, F. Arbeiter, P. Cara, et al. "IFMIF: overview of the validation activities". *Nucl. Fusion* 53, pp. 1-18, 2013.

- [25] P. Cara et.al, "The linear IFMIF prototype accelerator (LIPAC) design development under the european-japanese collaboration," in *Proc. of IPAC 2016*, 2016, pp. 985-988.

- [26] LIPAc Commisssioning Status. Available: <http://www.ifmif.org/>.

- [27] W. Kester, "Converting Oscillator Phase Noise to Time Jitter," Analog Devices Inc., Norwood, MA, USA, Tutorial MT-008, 2008.

Accepted Version